Новое поступление

Осень-зима 2017 длинная свободная вязаная накидка-пончо с рукавами летучая мышь

Ультразвуковой ионный скребок для глубокого очищения кожи лица перезаряжаемый

Conmoto летние белые сексуальные повседневные женские блузки уличная одежда

Женский трикотажный комплект из двух предметов элегантный винтажный Кардиган с

Искусственные реалистичные силиконовые формы для груди IBANBIA трансвеститные

Новинка осенне-зимнее женское черно-белое пальто стильная и удобная

Новый Птица Попугай Стенд Swing 1 шт. |

Характеристики

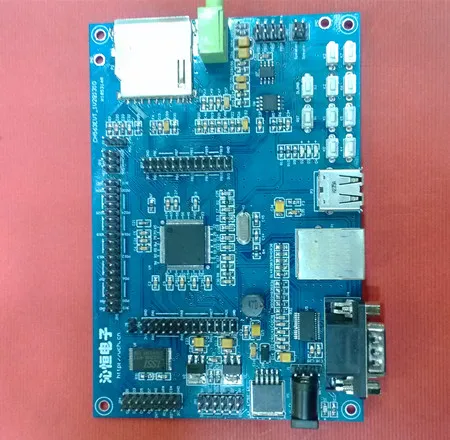

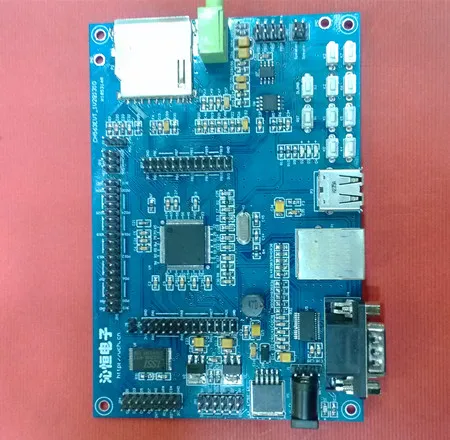

Для ARM9 комплект разработчика 32-битный микроконтроллер ARM CH563 Совет по развитию

История изменения цены

*Текущая стоимость 5 185,62 уже могла изменится. Что бы узнать актуальную цену и проверить наличие товара, нажмите "Добавить в корзину"

| Месяц | Минимальная цена | Макс. стоимость | Цена |

|---|---|---|---|

| Feb-18-2026 | 6585.20 руб. | 6717.46 руб. | 6651 руб. |

| Jan-18-2026 | 5341.12 руб. | 5448.97 руб. | 5394.5 руб. |

| Dec-18-2025 | 6481.35 руб. | 6611.11 руб. | 6546 руб. |

| Nov-18-2025 | 6429.66 руб. | 6558.66 руб. | 6493.5 руб. |

| Oct-18-2025 | 5133.37 руб. | 5236.58 руб. | 5184.5 руб. |

| Sep-18-2025 | 6326.46 руб. | 6453.79 руб. | 6389.5 руб. |

| Aug-18-2025 | 6274.93 руб. | 6399.6 руб. | 6336.5 руб. |

| Jul-18-2025 | 6222.92 руб. | 6346.7 руб. | 6284 руб. |

Описание товара

CH563 представляет собой 32 бит RISC снижена набор инструкций Процессор как ARM9 ядроКомандный набор совместим с ARMv5TE, поддерживает 16 бит с накатанной головкой инструкции и повышает DSP инструкции. Система по умолчанию работает на частоте 62,5 МГц, до 130 МГц. Высокоинтегрированные периферийные устройства, а также высокая производительность позволяют широко использовать их в различных встроенных приложениях.

Периферийный компонент CH563 содержит вспышку 480K, флеш-память 128K может динамически выделяться SRAM, 32K, EEPROM, высокоскоростной USB / 100M Ethernet хост/slave интерфейс, 2 SPI порта, 2 портов UART, 3 канала 10 бит ADC, 4 общего таймер, 8 бит параллельный интерфейс, 8/16/32 пассивный Intel время интерфейса шины, ISP интерфейс, ICE/JTAG в системном программировании и отладке интерфейса до 74 контактов общего назначения I/O.

Характеристика

Ядро:32 бит RISC инструкции комплект Процессор, совместимый с обшит тканью V5TE набор инструкций, поддерживает 16 бит с накатанной головкой и увеличивает DSP инструкция системаМаксимальная частота до

130 МГц.

Вспышка и RAM:Вспышка on-chip 480K, которая используется для сохранения кода программы и поддержки защиты записи, где 256K Используется для загрузчика. ВспышкаФлэш-память

Есть 100 тысяч, 20 лет, чтобы сохранить возможность стирания, поддержка обновления ICP/ISP.SRAM On-chip является общим для 128K, используется для буферизации программ и буферизации данных. Пользователи могут в соответствии с потребностями

Для самостоятельного распределения обычный метод: 32K,64K или 96K в качестве буфера prog ram, а остальное в качестве RAM данных.

EEPROM:Встроенный чип EEPROM 32K используется для сохранения нелетучих данных.

EthernetВстроенный MAC и DSP на основе 10/100Base-TX fast Ethernet оптический приемопередатчик (PHY), чтобы поддержать 10/100 Мбит/с на витую паруСетевая связь, одновременно

Позвольте IEEE, 802.3802.3u и FDDI-TP-PMD поддерживать функции Wake-On-LAN, чтобы отправлять и получать самостоятельно2K байта FIFO поддерживают DMA.

USB:Встроенный высокоскоростной usb-приемопередатчик (PHY) и usb-контроллер, поддержка USB 2, Совместимость с EHCI, поддержка master / slave / mode, поддержкаВысокая скорость/полная скорость/низкая скорость передачи

2K + 64 не зависит от байтов, байтов FIFO и поддерживает DMA.

SPI:2 группы SPI контроллера SPI0 и SPI1, скорость регулируется, до половины частоты системы SCLK, около 60 МГц, поддержка входного сигналаСимплексный мультиплексный выход.

SPI0 поддерживает режим Master/Slave Master - Slave, 32 уровня FIFO, поддерживает DMA;SPI1 поддерживает только режим хоста, FIFO уровень 16. UART: 2 группы совместимы с 16 c550 асинхронным UART последовательным портом, скорость регулируется, до одной 8 частоты системы SCLK составляет около 16 Мбит/с, набор поддерживает все Сигналы модема, FIFO, уровень 16 поддержка PECL вход;Другая группа поддерживает только CTS и RTS, но поддерживает nine bus address, автоматически сравнивает и серийный режим Сэр IrDA codec, 32 класс FIFO. ADC: 3 канала 10 бит A/D конвертер, частота дискретизации регулируется, до 1 м в секунду, величина 8 FIFO, поддержка повышения прерывания после ее прибытия, чтобы установить ссылку Два канала автоматического измерения, доступное программное обеспечение для алгоритма декодирования сигнала и поддержки DMA. Время: 4 набора таймера 28, поддержка ширины выборки входного сигнала/захвата сигнала (высокий/низкий/флип), поддержка PWM выхода, 8 FIFO, три группы поддержки DMA.Встроенный таймер 0/1 со специальным серийным декодированием CRC и дифференциальным входом PECL, может использоваться в оптоволоконной связи, скорость регулируется, до 117 Мбит/с, Поддержка DMA. Пассивная Параллель: обеспечивает последовательность пассивного параллельного порта Intel eight, удобную для передачи данных с внешними системами. Интерфейс шины: обеспечивают процессором Intel последовательность интерфейс шины, Поддержка 8-битных, 16-бит и 32-битный чтения и записи данных, чтения и записи ширина регулируется. Интерфейс отладки ICE/JTAG: Обеспечивает стандартный интерфейс тестирования ICE/JTAG/debug. Режим сна с низкой мощностью: поддерживает режим сна с низкой мощностью, поддерживает часть внешнего пробуждения GPIO. Чип ID: в зависимости от настроек чип с 64-разрядный уникальный ID идентификационный номер, в целях упрощения контактов удостоверений личности или шифрование данных. GPIO: Инкапсуляция LQFP128 обеспечивает до 74 контактов GPIO, часть контактов поддерживает выдвижные резисторы, вытяжной резистор, ввод Smith, два вида способности к вождению. Часть уровня поддержки или края прерывания GPIO, два уровня приоритета прерывания. Мощность поставки: Процессор диапазон рабочего напряжения: 1,65-1,95 V (+ / -0,15 V, 1,8 V);Ввода-вывода Диапазон напряжений: 3,0-3,6 V, 3,3 V + / - 10%), может принести часть порт ввода/вывода Напряжение 5 В.

Смотрите так же другие товары: